# Cell/B.E.を用いたステレオ PIV 計測の準リアルタイム処理

冨田明彦,加藤辰哉(株式会社フィックスターズ), 加藤裕之,藤田直行,渡辺重哉(宇宙航空研究開発機構)

# Quasi-real-time stereo PIV processing accelerated by Cell/B.E.

Akihiko Tomita, Tatsuya Kato (Fixstars Corporation) Hiroyuki Kato, Naoyuki Fujita, Shigeya Watanabe (JAXA)

#### **ABSTRACT**

Particle Image Velocimetry (PIV) is well established as a fluid dynamics measurement tool, being applied to many industrial wind tunnel applications for measuring distributed velocity fields. However, PIV processing, which is a calculation from seeding images acquired in experiments to velocity field distributions, is a very time-consuming one. Usually, PIV processing corresponding to 1,000 sets of seeding images consumes a few hours. Therefore, the existing system just records the seeding images in wind tunnel testing, after that, PIV processing from recorded images is carried out by 2 to 4 weeks. Because of this, acceleration of PIV processing is very important issue in the industrial wind tunnel applications. This paper shows the acceleration of PIV processing using the accelerator board "GigaAccel180" based on Cell/B.E. processor. This Cell/B.E. system outperformed the current cluster system more than 10 times in the processing speed.

### 1. はじめに

粒子画像流速測定法 (Particle Image Velocimetry; PIV) は、 流れ場の理解に優れた計測法のひとつとして、これまで、 数多くの実用風洞試験において活用されている<sup>1)</sup>。しかし ながら、PIV計測では、撮影されたシード画像から、速度 を算出するための処理(PIV 処理)に、非常に多くの時間を 要し、通常、風洞試験期間内での結果出力は困難である。 従来の実用風洞試験では、試験期間中はシード画像の取得 のみに専念し、試験終了後に PIV 処理を行い、結果出力は 2~4週間後となるため、結果出力までの時間を短縮するこ とが大きな課題となっている。JAXAでは、現在、EFD/ CFD融合に向けた試みとして、デジタル/アナログ・ハイブ リッド風洞の構築に向けた取り組みが行われている<sup>2)</sup>。こ の取り組みでは、アナログ風洞の画像計測データ処理高速 化を一つの課題としており、現在、流体画像計測技術で最 もデータ処理に時間を要しているのは、PIVであるため、 PIVデータ処理の高速化をターゲットに絞った検討を実施 している。

JAXA 風洞技術開発センターにおいて整備されているステレオ PIV システムは、商用 PIV システム(LaVision 社、DaVis Ver.7.2)をベースに構築されており、PC クラスタを利用することで、PIV 処理高速化を図っている。しかしながら、PC クラスタを用いた処理でも、現状、1 試験ケース(1,000 ベクトルマップ)の結果出力までには数時間を要するため、試験期間中は、一部データの処理に留まっている。

PIV 処理高速化の方法としては、アルゴリズム改良による演算量削減、一部ハードウェア置換を利用したソフトウェア高速化、全ハードウェア置換による高速化などが考えられる。

アルゴリズムを改良した場合、これまでの計測結果と親和性が低くなる可能性がある上、そういった同等のアルゴリズムが見つからない可能性がある。一方、全ハードウェアを専用のものに置換すれば格段に高い性能が得られるが、ハードウェアの調達コストが高い上、ソフトウェアの柔軟性が大きく損なわれる。アルゴリズム開発のリスクを軽減し、ソフトウェアの柔軟性を大きく損なわず、かつハードウェアの調達コストを抑制するため、Cell Broadband Engine

(以下、Cell/B.E.と略す) や  $GPU^{5}$ といったアクセラレータの 採用について検討した  $^{6}$ 。

相互相関処理に限定して評価した結果、Cell/B.E. 及びGPU ともに同程度の演算時間となることが確認された。開発効率、性能の両面から定性的な検討も行った結果、Cell/B.E. による PIV 処理システムの開発を進め、高速化を実現することに決定した。本報では、構築したシステムの構成と、性能測定の結果について報告する。

### 2. ハイブリッド風洞における PIV 処理高速化

図1に、ハイブリッド風洞システムの当初の適用先となる JAXA 2m×2m 遷音速風洞 (TWT1) における現状の PIV 計測時のタイムフローを示す。現状では、PIV 計測の画像取得終了後、取得画像の 5%程度のシード画像に対してのみ、計算負荷の比較的低い処理パラメータによるクイック処理を行い、取得データの健全性のみ確認する。試験期間終了後、2~4週間の時間をかけて、詳細検討に必要な正データを得るための PIV 処理を行う。従って、試験期間内に、PIV 計測結果を参照しながら、試験パラメータを再検討するといった作業は実質上、不可能な状況となっている。

| 項目        | 9:00 | 10:00 | 11:00    | 12:00 | 13:00   | 14:00 | 15:00 | 16:00         | 17:00 | 18:00 | 19:00    | 2~4週間 |

|-----------|------|-------|----------|-------|---------|-------|-------|---------------|-------|-------|----------|-------|

| 試験準備      |      |       |          |       |         |       |       |               |       |       |          |       |

| 通風試験      |      |       | <b>→</b> |       | _       |       |       | $\rightarrow$ |       |       |          |       |

| 画像データ取得   |      |       | <b></b>  |       |         |       |       | Î             |       |       |          |       |

| クイックデータ処理 |      |       |          | Î     |         |       |       |               |       |       | <b>†</b> |       |

| クイック結果可視化 |      |       |          |       | <b></b> |       |       |               |       |       | 1        |       |

| PIVデータ処理  |      |       |          |       |         |       |       |               |       |       |          | •••   |

| 結果可視化     |      |       |          |       |         |       |       |               |       |       |          | •••   |

図1 PIV 計測タイムフロー(現状)

図 1 のような状況に対して、ハイブリッド風洞システムにおける PIV 処理高速化では、PIV 処理の高速化により、図 2 のようなタイムフローの実現を目指した。このタイムフローでは、画像取得中、並行して、取得済み画像に対する PIV 処理を実施している。画像取得から 1~2 時間遅れ

で、計測結果を出力することにより、試験期間内に、PIV 計測結果を参照しながら、模型形態変更等の検討が可能と なる。このタイムフローを実現するためには、現在、結果 出力までに数時間要する PIV 処理を数分で完了させる必要 があり、現状に対して 10 倍以上の高速化が必要となる。

| 項目        | 9:00 | 10:00 | 11:00    | 12:00         | 13:00 | 14:00 | 15:00 | 16:00         | 17:00         | 18:00 | 19:00 | 2~4週間 |

|-----------|------|-------|----------|---------------|-------|-------|-------|---------------|---------------|-------|-------|-------|

| 試験準備      |      |       |          |               | •     |       |       |               |               |       |       |       |

| 通風試験      |      |       | <b>→</b> |               | _     |       |       | $\rightarrow$ |               |       |       |       |

| 画像データ取得   |      |       | <b>→</b> |               |       |       |       | $\uparrow$    |               |       |       |       |

| クイックデータ処理 |      |       |          |               |       |       |       |               |               |       |       |       |

| クイック結果可視化 |      |       |          |               |       |       |       |               |               |       |       |       |

| PIVデータ処理  |      |       |          | $\rightarrow$ |       |       |       |               | $\rightarrow$ |       |       |       |

| 結果可視化     |      |       |          | Î             |       |       |       |               |               |       |       |       |

図 2 PIV 計測タイムフロー(PIV 処理高速化後)

### 3. システム構成

#### 3.1. 制御システムと画像処理システムへの分離

既存のシステムでは、撮像用カメラの制御中は画像処理を行っていなかった。システム全体の高速化を考えた場合、単に画像処理そのものを高速化するだけでなく、撮像中も撮像し終えた画像から処理を開始することで、よりリアルタイムに近い処理が可能になると考えられる。

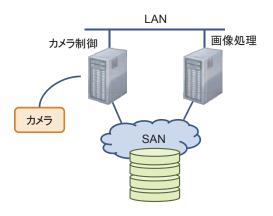

そこで、単一システムとして実現されていた制御機能と画像処理機能を、制御システムと画像処理システムに分離し、両システムから同一のストレージにアクセスできるよう SAN (Storage Area Network) を構築した(図3)。システム毎に機能を分離した独立のマシンを2台用意することにより、お互いの影響を最小限に抑えることが可能となる。ストレージは、両システムにファイバチャネルで接続され、制御信号の授受はギガビットイーサネットで行うものとした。

図3 システム全体構成

### 3.2. 画像処理システムの構成

画像処理システム用に Cell/B.E.が搭載されたアクセラレータ GigaAccel 180<sup>7)</sup> を準備した。 GigaAccel 180 はフィックスターズ社の製品で、PCI Express をインターフェースとしてホストワークステーションのマザーボードに接続される。マザーボードによっては、複数台搭載することも可能である。今回は、性能面も考慮して GigaAccel 180 を 2台搭載する構成とした。これを図 4 に示す。

GigaAccel180上ではOSが動作し、ホストCPUとは独立に動作させることが可能である。

\*PCIe : PCI Express

図4画像処理システム構成

### 4. ソフトウェア開発

### 4.1. ソフトウェア概要

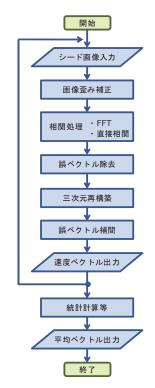

ステレオ PIV における処理手順を図5に示す。

図5 ステレオ PIV 処理フロー

ステレオ PIV では、2 台のカメラを駆使し粒子の移動量 を3次元ベクトルマップとして出力する。出力を得るため に、大きく2 段階の処理を行っている。

まず第1段階としてカメラ別の処理を行う。1台のカメラで撮像された2枚の時系列画像をシード画像として入力する。シード画像は、カメラの設置パラメータやレンズの歪みパラメータ(以降、カメラパラメータ)から、シード画像の歪みを補正する。補正された画像に対し相関処理を施し、粒子の移動ベクトルを算出する。算出された移動ベクトルから、フィルタを適用して誤ベクトルの除去

を行う。以上の処理をカメラ別に行うことで、2つの2次元ベクトルマップが得られる。

第2段階は、2つの2次元ベクトルマップから、3次元ベクトルマップを得る処理となる。カメラパラメータを用いて3次元再構築し、出力候補となる3次元ベクトルマップを算出する。候補となった3次元ベクトルマップに対し、欠落したデータを補うため、ベクトルの補間処理を行う。補間処理された3次元ベクトルマップをファイルに出力する。

最後に、画像の入力からベクトルマップの出力までを1 試験ケース分繰り返し、それらの統計をまとめ、平均ベクトルとして出力する。

各処理において候補となるアルゴリズムは複数存在するが、特に相関処理については、DaVis と同等と推定される高速フーリエ変換(以降、FFT)と、演算量は多いが FFT と比較してより正確な相関値が得られる直接相関の 2 通りを採用し、実装した。

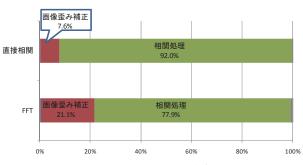

高負荷の処理を特定するため、作成したリファレンスコードに対し、プロファイリングを行った。結果を図 6 に示す。入力データは、2048x2048 画素の 12 ビットグレイスケールであり、画像歪み補正後の画像サイズは 4900x2533 画素である。測定条件は、相関窓サイズ 32x32 画素、50%オーバーラップとした。このとき、最も高い処理負荷を示したのは相関処理で、FFT 法で処理全体の 77%、直接相関法で処理全体の 92%の時間を費やしていた。その次に高い処理負荷をもつ演算は、7%から 21%を費やしている画像歪み補正であった。画像歪み補正の実行時間は同じだが、FFT 相関処理よりも直接相関処理の実行時間の方が長いため、相関処理の占める割合が高くなっている。

図6プロファイリング結果

### 4.2. 処理割り付け

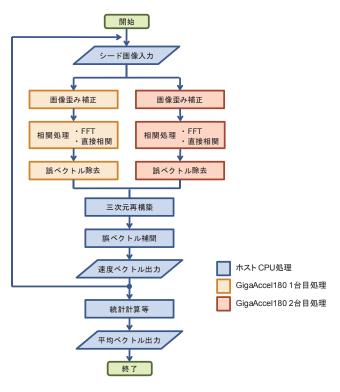

GigaAccel180 を採用した Cell/B.E.画像処理システムでは、ホスト CPU とアクセラレータである Cell/B.E.が独立に画像処理を実行可能であるため、ホスト側とアクセラレータ側とで処理を分担することにした。処理の割り付けを図 7 に示す。青で囲まれた処理がホスト CPU、赤、橙で囲まれた処理が 2台の GigaAccel180 に割り当てられていることを示す。

処理の割り付けに際し、プロファイリングに加え、データ転送量の検討も行った。データ転送量が多くなると、データ転送時間がボトルネックとなり、システム全体の性能を律速するからである。

アクセラレータシステムにおけるデータ処理方法は、アクセラレータ単体で処理する方法と、アクセラレータとホストマシンが協調して処理を行う方法の 2 つに大別される。プロファイリングの結果では、一部の処理が大部分の時間を占めているため、処理全体をアクセラレータに移植す

るより、一部の処理のみをアクセラレータに移植する方が、 性能・開発効率の両面において妥当である。

図 6 によれば、相関処理の実行時間が最も長いため、相 関処理の移植を最優先とした。相関処理の入力は画像デー タ、出力はベクトルデータである。処理により得られるベ クトルデータ量は、画像データ量と比較して各段に少ない。

2番目に実行時間の長い画像歪み補正処理への入力は、画像データ、出力も画像データである。処理の性質上、出力の画像データ量は入力の画像データ量よりも大きくなる。画像歪み補正処理の出力は、相関処理の入力となるため、両処理をアクセラレータに移植し、アクセラレータ上でデータを共有すれば余分なデータ転送をせずに済む。

一方、誤ベクトル除去処理は、処理全体に占める時間の割合が少ないが、アクセラレータで処理することとした。4.1. 節で記述した通り、誤ベクトル除去はカメラ別に処理可能である。つまり、相関処理から誤ベクトル除去処理までを図7のように並列に処理することができる。これにより、シード画像入力から速度ベクトル出力までのレイテンシをより小さくすることが期待できる。

並列処理のため、1台のカメラによる撮像画像処理を 1台の GigaAccel180 に割り当てた。ディスクからの撮像画像 読み込みと、3次元再構築以降の処理はホスト側で行うものとした。

図 7 処理割り付け

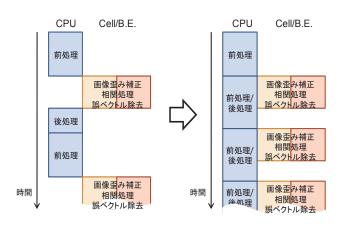

## 4.3. 処理のパイプライン化

図7に従い、アクセラレータによって一部の処理を高速 化すると、アクセラレータによる処理時間中、ホスト側の 演算リソースでは何も処理しない時間が発生する。この時 間に処理を割り当てることができれば、ホスト側の演算リ ソースを有効に利用でき、システム全体の性能も向上でき る。

そこで、一連の処理をパイプライン化することによりシステム全体の性能向上を図った。図 8 では、パイプライン

化する前の処理の様子を左側に、パイプライン化した後の 処理の様子を右に示した。

図8 処理のパイプライン化

図中の矩形は処理を表す。青で囲まれた処理がホスト側の演算リソースである CPU における処理を、橙、赤で囲まれた処理がアクセラレータ側の演算リソースである Cell/B.E. における処理を示している。矢印の通り下向きに経過時間を取っており、横に並んでいる処理が同時に実行されることを意味する。ホスト側の処理には細かな処理も含むため、簡単に前処理、後処理とした。前処理は主にシード画像をディスクから読み出し、処理可能な状態としてメモリ上に展開する処理である。後処理は主にアクセラレータで処理されたデータを受け、三次元再構築、誤べクトル補間し、算出された速度ベクトルをファイルへ書き出す処理である。

本システム開発の目的は、撮像された大量の画像を高速処理すること、つまりレイテンシの短縮とスループットの向上である。図 8 のようなパイプライン化は、主にシステムのスループット向上が期待できるため、システム開発の目的と合致する。

### 4.4. 関数レベルの高速化

図6に示したプロファイリング結果において計算負荷の高い関数について Cell/B.E. 上で高速化を行った。計算負荷が高いと判断したのは、画像歪み補正と、相関処理である。

特に相関処理が実行時間の 78%以上を占めているため、 使用頻度の高いパラメータをいくつか抽出し、各パラメー タに応じた高速化を施した。

### 4.4.1. 高速化の指針

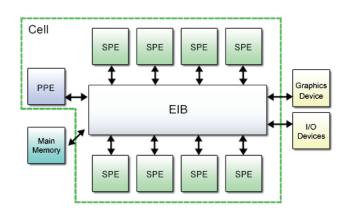

GigaAccel180 に搭載されている Cell/B.E. は図 9 のような構成をしている。

Cell/B.E は 1 基の制御系プロセッサコアである PPE (PowerPC Processor Element)と、8 基の演算系プロセッサコア SPE (Synergistic Processor Element)で構成されている。各プロセッサコアは EIB (Element Interconnect Bus)と呼ばれる高速バスで接続されている。

Cell/B.E. による高速化では、8 基ある SPE を効率良く利用することが肝要である。SPE を効率良く利用するためには、各 SPE で扱う演算量やデータ量が均一になるよう、データ割り当てを行うことが重要となる。

また、各 SPE は SIMD(Single Instruction Multiple Data) 演算器を搭載しており、SPE 内部でデータ並列処理が可能 である。

8基の SPE による並列演算に加え SPE 内部でも並列演算 することで、実行速度の大幅な向上が期待できる。

図9 Cell/B.E. の構成

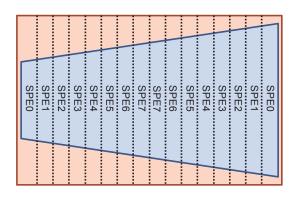

### 4.4.2. 画像歪み補正処理の高速化

画像歪み補正処理では、撮像で得られた画像をカメラの 設定パラメータを利用することにより、レンズによる歪み を補正しつつ、任意の視点から捉えた画像に変換する。

変換により、有効画素の領域が矩形からおおよそ台形へ 変形する。演算量削減のため有効画素領域のみ演算する場 合、確保された領域が全て演算対象とならず、演算対象と なるデータが偏在することを意味する。

図 10 画像歪み補正処理の演算コア割り当て

偏在した演算対象データを均一化するため、図 10 のように領域分割を行い、各 SPE へ割り当てた。図中、実線長方形で囲まれた部分が確保された領域で、実線台形で囲まれた部分が演算対象領域である。縦に走る破線が領域の分割線であり、各領域に記されている "SPE0", "SPE1",..., "SPE7"が該当領域を処理する SPE となる。

実装では全 16 領域に分割しており、各 SPE に 2 つの領域を割り当てている。有効画素領域がほぼ台形になることを利用して、割り当てられた 2 つの領域における有効画素の領域が、どの SPE でもほぼ同面積となるようにした。これにより、各 SPE で扱うデータ量、演算量が均一化され、SPE の効率的な利用が期待できる。

画像歪み補正処理は、ピクセル単位で独立であるため、 SIMD 演算が可能である。そこで実装においても SIMD 命 令を使用したデータ並列化を施した。

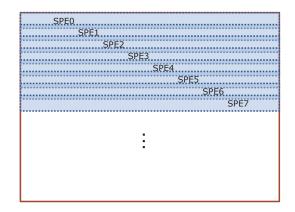

### 4.4.3. 相関処理の高速化

高速化対象の相関処理では、複数の検査領域に対し、指 定されたパラメータに基づいた探査領域をそれぞれ切り出 し、それらに対して相関演算を行う。

相関演算量が均一化されるよう、各 SPE に検査領域を割り当てる。検査領域に対応する探査領域の割り当ての一例を図 11 に示す。実線長方形で囲まれた領域が探査画像であり、破線長方形で囲まれた領域が SPE に割り当てられる領域である。パラメータに依存するが、各 SPE が探査対象とする領域に重複が発生する場合がある。

相関処理においても画像歪み補正処理と同様に SIMD 演算を適用できるため、実装では SIMD 命令を使用したデータ並列化を施した。

図11 相関処理の演算コア割り当て

### 5. 評価結果

これまで単一だったシステムを制御システムと画像処理 システムに分離した効果の評価結果を表1に示す。

表1 システム分離の効果

|      | FF    | -T    | 直接相関  |       |  |  |

|------|-------|-------|-------|-------|--|--|

|      | 32x32 | 64×64 | 32x32 | 64×64 |  |  |

| 単独処理 | 1     | 1     | 1     | 1     |  |  |

| 協調処理 | 1.04  | 1.10  | 1.00  | 1.00  |  |  |

画像処理単体で実行した時間を1とした場合に、撮像システムと画像処理システムを同時に動作させたときの実行時間を割合として示したものである。値が1に近いほど、2つのシステムは互いに高い独立性を持ち、高速化に寄与することを示す。表では、基準となる画像処理単体での実行を単独処理として上段に、比較対象となる制御システムとの協調実行を協調処理として下段に示した。

処理は 50 ベクトルマップを出力するステレオ PIV を想定し、相関演算の種類を FFT、直接相関の 2 種類、相関窓サイズも 32x32 画素、64x64 画素の合計 4 パタンで測定を行った。なお、オーバーラップ率は全て 50%である。入力画像サイズは、プロファイリング時と同様に 2048x2048 画素、画像歪み補正後は 4900x2533 画素を処理している。

表1から、測定した全パラメータに対し、数%以内で収まっており、高い独立性を保つことが確認できた。なお、制御システムと画像処理システムの同時稼働時、つまり画像処理を実行すると同時に、シード画像を取得しても、制御システム側のシード画像取得レートは低下しなかった。

画像処理システムは高い独立性を持つため、システム単体での高速化が、撮像システムを含めた全システムの高速化をもたらす。そこで、画像処理システムついて、クラスタを使用した既存システムと、新規に採用した Cell/B.E.システムにおいて、50 ベクトルマップを出力するためのステレオ PIV 処理時間を測定した。評価に使用した既存クラスタシステムのハードウェア環境を表 2 に、Cell/B.E.システムのハードウェア環境を表 3 に示す。

表2 クラスタシステム

| システム | ノード数   | 7                                                |  |  |  |  |  |

|------|--------|--------------------------------------------------|--|--|--|--|--|

| ンステム | ノード間接続 | Gigabit Ethernet                                 |  |  |  |  |  |

| 各ノード | CPU    | Pentium D 950 @3.4GHz /<br>Pentium D 820 @2.8GHz |  |  |  |  |  |

|      | メモリ    | 0.5GB                                            |  |  |  |  |  |

表 3 Cell/B.E. システム

|           | ホスト     | -                                            |  |  |  |  |  |

|-----------|---------|----------------------------------------------|--|--|--|--|--|

| システム      | アクセラレータ | Cell/B.E. アクセラレータ<br>GigaAccel180 2台         |  |  |  |  |  |

| ホスト       | CPU     | Dual-Core AMD Opteron 2220<br>@2.8GHz, 2-way |  |  |  |  |  |

|           | メモリ     | 4GB                                          |  |  |  |  |  |

| Cell/B.E. | CPU     | PowerXCell8i 2.8GHz                          |  |  |  |  |  |

| アクセラレータ   | メモリ     | 4GB                                          |  |  |  |  |  |

既存のクラスタシステムは、7つのノードで構成され、ノード間は Gigabit Ethernet で接続されている。一方、Cell/B.E. システムはホストワークステーション筐体内にアクセラレータが収納できる構成になっており、PCI Expressで接続されている。アクセラレータには 2.8GHz で動作する Cell/B.E. と、4GB のメモリが搭載されている。

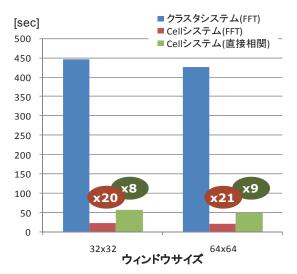

既存のクラスタシステムにおいて DaVis により処理した場合と、Cell/B.E.システムにおいて高速化されたプログラムで処理した場合について 1000 ベクトルマップの出力までにかかる時間を計測した。相関演算の種類は FFT 及び直接相関とし、相関演算種毎に相関窓サイズを 32x32 画素 50%オーバーラップ、64x64 画素 50%オーバーラップと複数のパラメータを設定し測定した。ただし DaVis における相関演算は FFT しかないため、直接相関による実行時間は測定しない。測定結果を表 4に示す。

表 4 PIV 処理実行時間一覧

|          | FF    | -T    | 直接相関  |       |  |  |  |

|----------|-------|-------|-------|-------|--|--|--|

|          | 32×32 | 64×64 | 32x32 | 64×64 |  |  |  |

| クラスタシステム | 446   | 426   | -     | -     |  |  |  |

| Cellシステム | 22    | 20    | 57    | 49    |  |  |  |

| _        |       |       |       |       |  |  |  |

[sec]

既存クラスタシステムでは FFT 法を適用した場合、処理に 400 秒以上かかっていたが、Cell/B.E. システムでは FFT 法、直接相関法共に数十秒程度に短縮されている。特に DaVis と同等のアルゴリズムで処理した場合、20 倍高速化できた(図 12)。FFT 法よりも演算量が大きい直接相関法を適用した場合でも、既存クラスタシステムにおける DaVis 実行時間と比較して、8 倍程度高速化できていることが確認できた(図 12)。

図中、青のグラフはクラスタシステムにおける実行時間を、赤のグラフは Cell/B.E.システムで FFT 法を選択したときの実行時間を、緑のグラフは Cell/B.E.システムで直接相関法を選択したときの実行時間をそれぞれ表す。

ただし、この実行時間には統計計算を実行する時間は含まれていない。

図 12 PIV 処理実行時間のシステム別比較

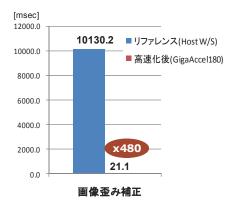

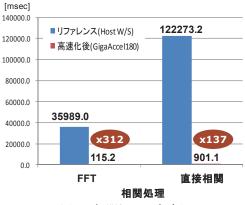

画像処理の高速化工程では、機能毎にリファレンスコードを記述し、それを基に高速化を行った。機能別にリファレンスの実行時間と、高速化後の実行時間を比較することで高速化の効果を評価する。

高速化対象とした画像歪み補正処理の比較を図13に、相関処理の比較を図14に示す。図中、青のグラフはリファレンスの実行時間を、赤のグラフは高速化後の実行時間を表す。また、図中に記された時間は、1ベクトルマップを出力するための処理時間を表す。測定に際し、特に使用頻度の高い条件である、相関窓サイズ32x32画素、50%オーバーラップを設定した。

画像歪み補正処理の高速化では、Cell/B.E. の演算リソースを有効に利用する実装に加え、演算量そのものの削減も行った。その結果、リファレンスと比較して480倍もの高速化を達成できた。

相関処理については、FFT 法、直接相関法を評価した。 FFT 法については 312 倍、直接相関法については 137 倍の 高速化を達成した。

図 13 画像歪み補正処理の高速化

図 14 相関処理の高速化

### 6. まとめ

ステレオ PIV 処理の高速化にあたり、画像処理システムのアクセラレータとして Cell/B.E.が搭載された GigaAccel-180 を採用した。設計では、単に関数そのものの高速化だけでなく、システムリソース全体の有効利用も考慮した。

その結果、目標である既存クラスタシステム比 10 倍以上の性能も達成することができた。最も使用頻度の高い、FFT 相関演算 (相関 32x32 画素、50%オーバーラップ) において、50ベクトルマップを得るためのステレオ PIV 処理に22 秒、1 秒あたりに換算して約 2.3 ベクトルマップ分の処理をすることが可能となり、リアルタイムに近い速度での処理を実現した。

今回の開発では、実用にたえるステレオ PIV 処理の実装と、リアルタイム処理システムが構築可能であることの実証を目的とした。そのため、実装はステレオ PIV 処理の中でも基本的な部分が対象となっている。

しかしながら、より高精度で柔軟な解析を行うには、更なる機能拡張が必要である。以上の点を考慮した上で、今後も Cell/B.E.アクセラレータの性能を十分に引き出せるような実装を検討し、開発を進めていく予定である。

### 謝辞

ステレオ PIV 処理の実装、高速化の検討を進めるにあたり、ご協力いただいた JAXA 小池俊輔氏に深く感謝いたします。

### 参考文献

- 1) 渡辺他, "大型風洞用粒子画像流速測定(PIV)システムの 開発," 第41 回飛行機シンポジウム 講演集, 1C8, 2003.

- 2) 渡辺他, "JAXA における EFD/CFD 融合に向けた試み," 第 40 回流体力学講演会/航空宇宙数値シミュレーション技術シンポジウム 2008 講演集, 1C12, 2008.

- Mark A. P., and Thomas H., "Processing High-Speed Stereo Particle Image Velocimetry Data with an Integrated Cluster Supercomputer," AIAA Paper 2007-51, 2007.

- Haiqian Y., et al, "Real-time Particle Image Velocimetry for Feedback Loops Using FPGA Implementation," AIAA Paper 2005-445, 2005.

- 5) Thomas S., and Rüdiger Westermann, "GPU-PIV," Proceedings of the Vision, Modeling, and Visualization Conference, pp.151-158, 2004.

- 6) 加藤他, "Cell及びGPGPUによるPIV処理高速化," 第41 回流体力学講演会 講演集, 1C10, 2009.

- 7) 株式会社フィックスターズ, "GigaAccel180", http://www.fixstars.com/products/gigaaccel180/index.html